- 您现在的位置:买卖IC网 > Sheet目录327 > HW-V5-ML561-UNI-G (Xilinx Inc)EVALUATION PLATFORM VIRTEX-5

�� �

�

�

�R�

�?�

�Test� Setup�

�strobe,� a� random� value� can� be� applied� to� data� bits� from� one� cycle� to� another.� A� 63-bit�

�PRBS6� (1)� (PRBS� of� order� 6)� test� pattern� stimulus� is� used� for� this� analysis.� The� value� of�

�this� PRBS6� string� is� 63’h03F5_66ED_2717_9461� ,� that� is:�

�63’b000001111110101011001101110110100100111000101111001010001100001� .�

�The� HyperLynx� stimulus� setup� is� for:� a� 2-sequence� repeat,� 10� bits� skipped,� 1� eye,� and�

�0%� jitter.�

�Test� criteria�

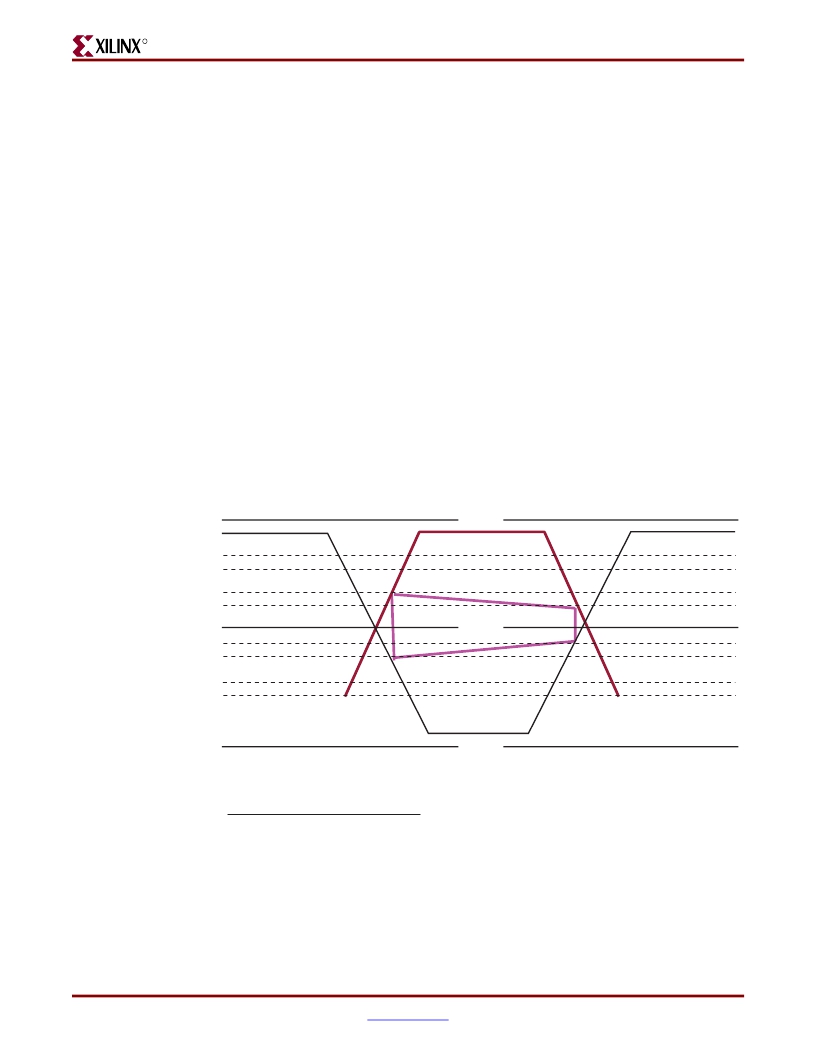

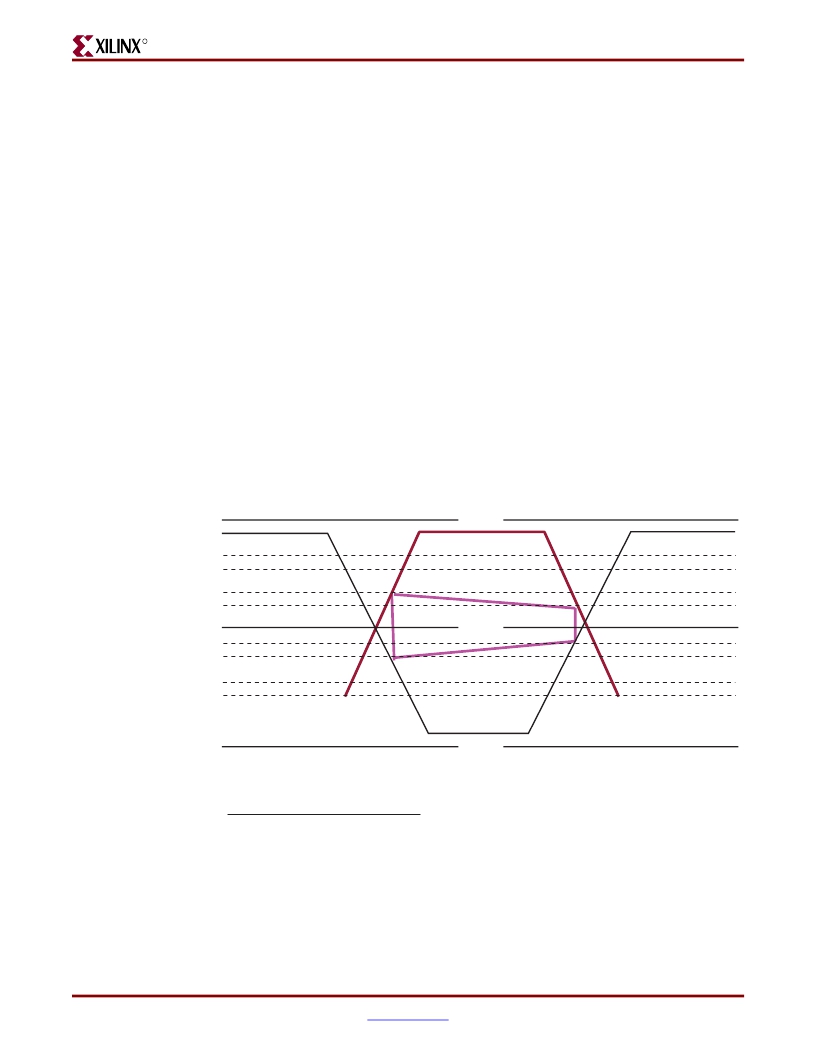

�Quality� of� a� signal� is� measured� in� terms� of� the� opening� of� the� signal� eye� at� the� receiver�

�input� for� both� the� amplitude� and� the� width.� DDR2� SDRAM� (Component� and� DIMM)�

�interfaces� utilize� the� SSTL_18� I/O� standard,� and� the� QDRII� SRAM� interface� utilizes�

�the� HSTL� 1.8V� I/O� standard.� For� each� of� these� two� I/O� standards,� the� eye� mask� is�

�defined� by� the� trapezoid� enclosed� by� the� following� four� voltage� thresholds� at� the�

�receiver� input:�

�?�

�?�

�?�

�?�

�VIH(ac)-min� at� the� rising� edge�

�VIH(dc)-min� at� the� falling� edge�

�VIL(dc)-max� at� the� rising� edge�

�VIL(ac)-max� at� the� falling� edge�

�Refer� to� Figure� 7-1� for� the� definition� of� voltage� levels� with� regard� to� the� trapezoidal�

�eye� mask.� Refer� to� “Terminology,”� page� 9� for� definitions� of� the� voltage� thresholds.�

�Because� the� HyperLynx� SI� simulation� software� does� not� support� a� trapezoidal� mask�

�definition,� two� separate� triangular� masks� for� VIH� and� VIL� are� defined,� as� shown� in�

��VDDQ�

�VOH(dc)�

�VIH(dc)�

�VIL(dc)�

�VREF�

�VIH(ac)�

�VIL(ac)�

�VOH(ac)�

�VOL(ac)�

�VOL(dc)�

�VSS�

�UG199_c7_01_062707�

�Figure� 7-1:�

�Single� Trapezoid� Eye� Mask� Definition�

�1.� A� maximal-length� PRBS� test� sequence� of� order� n� generates� all� (2� n� –� 1),� n-bit� combinations� of� test� sequences�

�(except� all� 0s).� Thus� the� test� sequence� contains� one� n-bit� long� consecutive� string� of� 1s� and� two� (n-1)-bit� long�

�consecutive� strings� of� 0s.� With� the� PRBS6� test� pattern,� at� the� highest� test� frequency� of� 333� MHz� (that� is,� the� bit�

�time� is� 1.5� ns),� measurements� in� this� setup� result� in� a� maximum� settling� time� of� (1.5� ns� *� 5)� =� 7.5� ns� for� a� logic�

�Low,� and� a� maximum� settling� time� of� (1.5� ns� *� 6)� =� 9� ns� for� a� logic� High.� 7.5� ns� is� sufficient� time� for� the� test�

�signal� to� reach� a� steady� state� before� the� next� transition.� Thus� a� PRBS� test� pattern� of� higher� order,� such� as� 7� or�

�9,� does� not� change� the� eye� pattern,� as� proven� by� sample� simulation� of� one� test� signal� with� PRBS6,� PRBS7,� and�

�PRBS9� stimuli.�

�Virtex-5� FPGA� ML561� User� Guide�

�UG199� (v1.2.1)� June� 15,� 2009�

��57�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

I-JET

JTAG ARM DEBUGGING PROBE

IAC24A

INPUT MODULE AC 5MA 24VDC

IAC5EQ

INPUT MODULE AC 10MA 5VDC

IB8RM

SURGE SUPP 8OUT 12'CORD W/REMOTE

IBAR12-20T

SURGE SUPPRSSR 20A 12OUT RACKMNT

IBAR12/20ULTRA

SURGE SUPPRSSR 20A 12OUT RACKMNT

IBAR12ULTRA

SURGE SUPPRSSR 15A 12OUT RACKMNT

IBAR12

SURGE SUPPRSSR 15A 12OUT RACKMNT

相关代理商/技术参数

HW-V5-ML561-UNI-G-J

功能描述:EVALUATION PLATFORM VIRTEX-5 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Virtex®-5 LXT 产品培训模块:Blackfin® Processor Core Architecture Overview

Blackfin® Device Drivers

Blackfin® Optimizations for Performance and Power Consumption

Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA

HW-V5-PCIE2-UNI-G

功能描述:KIT DEV PCIEXPRESS GTX VIRTEX5 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Virtex® -5 产品培训模块:Blackfin® Processor Core Architecture Overview

Blackfin® Device Drivers

Blackfin® Optimizations for Performance and Power Consumption

Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA

HW-VID-KIT

功能描述:可编程逻辑 IC 开发工具 Lattice Video Interface Kit

RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压:

HW-VL1

制造商:IDEC CORPORATION 功能描述:BARRIER

HW-VL2

制造商:IDEC Corporation 功能描述:COVER;HW FNGR SAFE CONTAC CVR 制造商:IDEC CORPORATION 功能描述:HW FNGR SAFE CONTAC CVR

HW-VL3

制造商:IDEC Corporation 功能描述: 制造商:IDEC Corporation 功能描述:Replacs TW-VL3 FNGR SAF

HWW-X030T-10015Z-H1

制造商:P-TEC 制造商全称:P-tec Corporation 功能描述:X30T RGB LED Wall Washers

HWW-X030T-10015Z-H2

制造商:P-TEC 制造商全称:P-tec Corporation 功能描述:X30T RGB LED Wall Washers